के तपाईंलाई बहु-तह पीसीबी डिजाइन गर्दा EMI समस्या कसरी समाधान गर्ने थाहा छ?

मलाई भन्न देउ!

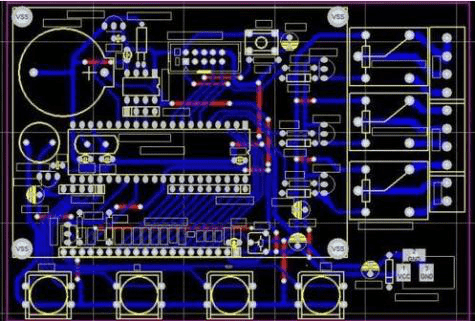

EMI समस्याहरू समाधान गर्ने थुप्रै तरिकाहरू छन्।आधुनिक EMI दमन विधिहरू समावेश छन्: EMI दमन कोटिंग प्रयोग गरेर, उपयुक्त EMI दमन भागहरू र EMI सिमुलेशन डिजाइन चयन गर्नुहोस्।सबैभन्दा आधारभूत PCB लेआउटमा आधारित, यो पेपरले EMI विकिरण र PCB डिजाइन कौशल नियन्त्रणमा PCB स्ट्याकको कार्यलाई छलफल गर्दछ।

पावर बस

IC को आउटपुट भोल्टेज जम्प IC को पावर पिन नजिकै उपयुक्त क्यापेसिटन्स राखेर छिटो गर्न सकिन्छ।तर, यो समस्याको अन्त्य भने होइन ।क्यापेसिटरको सीमित फ्रिक्वेन्सी प्रतिक्रियाको कारणले, पूर्ण फ्रिक्वेन्सी ब्यान्डमा आईसी आउटपुट सफा रूपमा ड्राइभ गर्न आवश्यक हार्मोनिक शक्ति उत्पन्न गर्न क्यापेसिटरको लागि असम्भव छ।थप रूपमा, पावर बसमा बनाइएको क्षणिक भोल्टेजले डिकपलिंग पथको इन्डक्टन्सको दुबै छेउमा भोल्टेज ड्रप निम्त्याउँछ।यी क्षणिक भोल्टेजहरू मुख्य सामान्य मोड EMI हस्तक्षेप स्रोतहरू हुन्।हामी कसरी यी समस्याहरू समाधान गर्न सक्छौं?

हाम्रो सर्किट बोर्डमा IC को अवस्थामा, IC वरपरको पावर लेयरलाई राम्रो उच्च-फ्रिक्वेन्सी क्यापेसिटरको रूपमा मान्न सकिन्छ, जसले सफा आउटपुटको लागि उच्च-फ्रिक्वेन्सी ऊर्जा प्रदान गर्ने अलग क्यापेसिटरद्वारा चुहावट भएको ऊर्जा सङ्कलन गर्न सक्छ।थप रूपमा, राम्रो पावर लेयरको इन्डक्टन्स सानो हुन्छ, त्यसैले इन्डक्टरद्वारा संश्लेषित गरिएको क्षणिक संकेत पनि सानो हुन्छ, जसले गर्दा सामान्य मोड EMI कम हुन्छ।

निस्सन्देह, पावर सप्लाई लेयर र आईसी पावर सप्लाई पिन बीचको जडान सम्भव भएसम्म छोटो हुनुपर्छ, किनभने डिजिटल सिग्नलको बढ्दो किनारा छिटो र छिटो छ।यसलाई सीधै प्याडमा जडान गर्न राम्रो छ जहाँ आईसी पावर पिन अवस्थित छ, जसलाई छुट्टै छलफल गर्न आवश्यक छ।

साझा मोड EMI नियन्त्रण गर्नको लागि, पावर लेयर राम्रोसँग डिजाइन गरिएको पावर लेयरहरूको जोडी हुनुपर्दछ जसले डिकपल गर्न मद्दत गर्दछ र पर्याप्त रूपमा कम इन्डक्टन्स हुन्छ।कतिपयले सोध्न सक्छन्, कति राम्रो छ ?जवाफ पावर तह, तहहरू बीचको सामग्री, र अपरेटिङ फ्रिक्वेन्सी (जस्तै, आईसी वृद्धि समयको प्रकार्य) मा निर्भर गर्दछ।सामान्यतया, पावर लेयरहरूको स्पेसिङ 6mil हुन्छ, र इन्टरलेयर FR4 सामाग्री हो, त्यसैले पावर लेयरको प्रति वर्ग इन्च बराबरको क्यापेसिटन्स लगभग 75pF हुन्छ।जाहिर छ, लेयर स्पेसिङ जति सानो हुन्छ, कैपेसिटन्स त्यति ठूलो हुन्छ।

त्यहाँ 100-300ps को वृद्धि समय संग धेरै यन्त्रहरू छैनन्, तर IC को हालको विकास दर अनुसार, 100-300ps को दायरा मा वृद्धि समय संग यन्त्रहरूले उच्च अनुपात ओगटेको छ।100 देखि 300 PS राइज टाइम भएका सर्किटहरूका लागि, 3 मिल लेयर स्पेसिङ अब धेरैजसो अनुप्रयोगहरूमा लागू हुँदैन।त्यस समयमा, इन्टरलेयर स्पेसिङ 1mil भन्दा कम भएको डेलामिनेशन टेक्नोलोजी अपनाउनु आवश्यक छ, र उच्च डाइलेक्ट्रिक स्थिर सामग्रीको साथ FR4 डाइलेक्ट्रिक सामग्री प्रतिस्थापन गर्न आवश्यक छ।अब, सिरेमिक र पोटेड प्लास्टिकले 100 देखि 300ps राइज टाइम सर्किटहरूको डिजाइन आवश्यकताहरू पूरा गर्न सक्छ।

यद्यपि नयाँ सामग्री र विधिहरू भविष्यमा प्रयोग गर्न सकिन्छ, सामान्य 1 देखि 3 एनएस राइज टाइम सर्किटहरू, 3 देखि 6 मिलि लेयर स्पेसिङ, र FR4 डाइलेक्ट्रिक सामग्रीहरू सामान्यतया उच्च-अन्त हार्मोनिक्स ह्यान्डल गर्न र क्षणिक संकेतहरूलाई पर्याप्त कम बनाउन पर्याप्त हुन्छन्। , सामान्य मोड EMI धेरै कम गर्न सकिन्छ।यस पेपरमा, PCB लेयर्ड स्ट्याकिंगको डिजाइन उदाहरण दिइएको छ, र लेयर स्पेसिङ 3 देखि 6 mil मानीन्छ।

विद्युत चुम्बकीय परिरक्षण

सिग्नल राउटिङ बिन्दुबाट, पावर लेयर वा ग्राउन्ड प्लेनको छेउमा रहेका सबै सिग्नल ट्रेसहरू एक वा बढी तहहरूमा राख्नु राम्रो लेयरिङ रणनीति हुनुपर्छ।पावर सप्लाईको लागि, पावर लेयर ग्राउन्ड प्लेनसँग जोडिएको राम्रो लेयरिङ रणनीति हुनुपर्छ, र पावर लेयर र ग्राउन्ड प्लेन बीचको दूरी सकेसम्म सानो हुनुपर्छ, जसलाई हामी "लेयरिङ" रणनीति भन्छौं।

PCB स्ट्याक

कस्तो प्रकारको स्ट्याकिंग रणनीतिले EMI लाई ढाल र दबाउन मद्दत गर्न सक्छ?निम्न स्तरित स्ट्याकिङ योजनाले एक तहमा विद्युत आपूर्ति प्रवाह प्रवाह गर्दछ र एकल भोल्टेज वा बहु भोल्टेजहरू एउटै तहको विभिन्न भागहरूमा वितरित हुन्छन् भन्ने मानिन्छ।बहु शक्ति तहहरूको मामला पछि छलफल गरिनेछ।

4-प्लेट प्लेट

4-प्लाई ल्यामिनेटहरूको डिजाइनमा केही सम्भावित समस्याहरू छन्।सबै भन्दा पहिले, संकेत तह बाहिरी तहमा र पावर र ग्राउन्ड प्लेन भित्री तहमा भए तापनि, पावर तह र ग्राउन्ड प्लेन बीचको दूरी अझै धेरै ठूलो छ।

यदि लागत आवश्यकता पहिलो हो भने, परम्परागत 4-प्लाई बोर्डको लागि निम्न दुई विकल्पहरू विचार गर्न सकिन्छ।तिनीहरू दुवैले EMI दमन कार्यसम्पादन सुधार गर्न सक्छन्, तर तिनीहरू केवल बोर्डमा कम्पोनेन्टहरूको घनत्व पर्याप्त मात्रामा कम भएको र कम्पोनेन्टको वरिपरि पर्याप्त क्षेत्र (बिजुली आपूर्तिका लागि आवश्यक तामाको कोटिंग राख्न) भएको अवस्थामा मात्र उपयुक्त हुन्छन्।

पहिलो रुचाइएको योजना हो।PCB को बाहिरी तहहरू सबै तहहरू हुन्, र बीचको दुई तहहरू सिग्नल / पावर तहहरू हुन्।सिग्नल तहमा रहेको पावर सप्लाई फराकिलो लाइनहरूद्वारा रुट गरिएको छ, जसले पावर सप्लाई करन्टको मार्ग प्रतिबाधा कम र सिग्नल माइक्रोस्ट्रिप पथको प्रतिबाधा कम बनाउँछ।EMI नियन्त्रणको परिप्रेक्ष्यमा, यो उपलब्ध उत्तम 4-तह पीसीबी संरचना हो।दोस्रो योजनामा, बाहिरी तहले शक्ति र जमीन बोक्छ, र बीचको दुई तहले संकेत बोक्छ।परम्परागत 4-तह बोर्डको तुलनामा, यो योजनाको सुधार सानो छ, र इन्टरलेयर प्रतिबाधा परम्परागत 4-तह बोर्डको रूपमा राम्रो छैन।

यदि तार प्रतिबाधा नियन्त्रण गर्न हो भने, माथिको स्ट्याकिङ योजनाले पावर सप्लाई र ग्राउन्डिङको तामा टापु अन्तर्गत तारहरू राख्न धेरै सावधान हुनुपर्छ।थप रूपमा, पावर सप्लाई वा स्ट्र्याटममा रहेको तामाको टापुलाई DC र कम फ्रिक्वेन्सी बीचको जडान सुनिश्चित गर्न सकेसम्म एक अर्कासँग जोडिएको हुनुपर्छ।

6-प्लेट प्लेट

यदि 4-तह बोर्डमा घटकहरूको घनत्व ठूलो छ भने, 6-तह प्लेट राम्रो छ।यद्यपि, 6-लेयर बोर्डको डिजाइनमा केही स्ट्याकिंग योजनाहरूको ढाल प्रभाव पर्याप्त छैन, र पावर बसको क्षणिक संकेत घटाइएको छैन।दुई उदाहरण तल चर्चा गरिएको छ।

पहिलो अवस्थामा, बिजुली आपूर्ति र जमीन क्रमशः दोस्रो र पाँचौं तहमा राखिएको छ।तामाले ढाकिएको बिजुली आपूर्तिको उच्च प्रतिबाधाको कारण, यो साझा मोड EMI विकिरण नियन्त्रण गर्न धेरै प्रतिकूल छ।यद्यपि, संकेत प्रतिबाधा नियन्त्रणको दृष्टिकोणबाट, यो विधि धेरै सही छ।

दोस्रो उदाहरणमा, पावर सप्लाई र ग्राउन्ड क्रमशः तेस्रो र चौथो तहमा राखिएको छ।यो डिजाइनले पावर सप्लाईको तामाले ढाकिएको प्रतिबाधाको समस्या समाधान गर्छ।लेयर 1 र लेयर 6 को खराब इलेक्ट्रोम्याग्नेटिक शिल्डिंग कार्यसम्पादनको कारण, भिन्नता मोड EMI बढ्छ।यदि दुई बाहिरी तहहरूमा सिग्नल लाइनहरूको संख्या न्यूनतम छ र रेखाहरूको लम्बाइ धेरै छोटो छ (सङ्केतको उच्चतम हार्मोनिक तरंग लम्बाइको 1 / 20 भन्दा कम), डिजाइनले भिन्नता मोड EMI को समस्या समाधान गर्न सक्छ।परिणामहरूले देखाउँदछ कि भिन्नता मोड EMI को दमन विशेष गरी राम्रो हुन्छ जब बाहिरी तह तामाले भरिएको हुन्छ र तामाले ढाकिएको क्षेत्र ग्राउन्ड गरिएको हुन्छ (प्रत्येक 1 / 20 तरंग लम्बाइ अन्तराल)।माथि उल्लेख गरिए अनुसार, तामा राखिएको हुनुपर्छ

पोस्ट समय: जुलाई-29-2020